|

|

CP/M 50, a 50MHz 2x1 inch CP/M computer

The idea was to design and build a small CP/M computer using readily available parts. This page provides an overview of the board design and software. Interested readers can find more detail in the schematic and source code referenced at the end of this page.

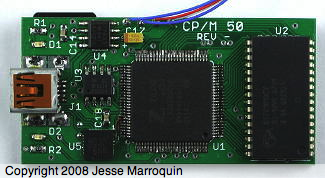

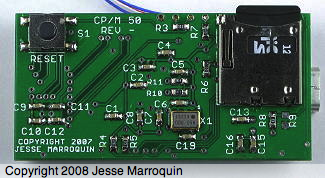

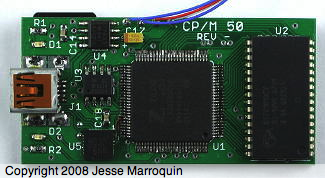

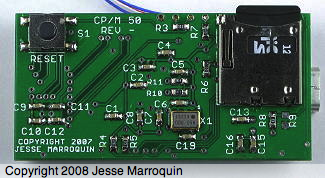

The images below show the top and bottom sides of the completed design. The board is 2 inches wide by 1 inch tall. The four wires connected to the board are temporary and used for programming the Z8 microcontroller.

|

|

Hardware

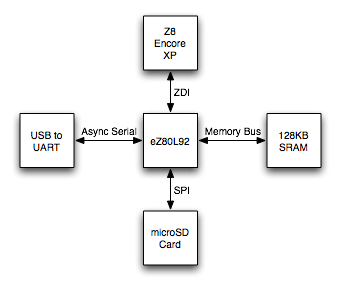

At the core of the design is a ZiLOG eZ80L92 processor running at 50MHz. A single 128KB 12ns SRAM provides system memory. Using 12ns SRAM allows the external bus to run with zero wait states. A microSD card connected to the L92's SPI bus provides disk storage. A USB to UART bridge connected to one of the L92's UARTs serves as a serial console. A ZiLOG Z8 Encore XP microcontroller bootstraps the system by loading a bootstrap image from its internal flash into the external SRAM of the L92 using the ZDI debug interface. A 3.3V LDO regulator powers the design from the USB bus. Below is a block diagram of the system.

Software

The board runs CP/M 2.2 consisting of a custom BIOS, or CBIOS, and the standard distribution of CCP and BDOS. The primary function of the CBIOS is to provide a console interface via one of the L92's serial ports and disk emulation via SPI and a microSD card. The microSD card provides four 8MB drives. A sector blocking and de-blocking algorithm enhances disk I/O performance. Terminal I/O makes use of the L92's 16-byte receive and transmit FIFOs.

Operation

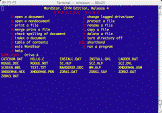

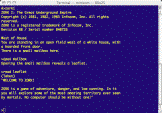

Below are screenshots of the system boot message and several applications. Click a screenshot for a higher-resolution image.

|

|

|

|

|

| Boot Message | Ladder | SuperCalc2 | WordStar | Zork I |

Resources

The "The Unofficial CP/M Web site" contains a wealth of information about Digital Research and CP/M. Various CP/M sources and manuals can be found there.